10G以太网接口简介

1、10G以太网结构

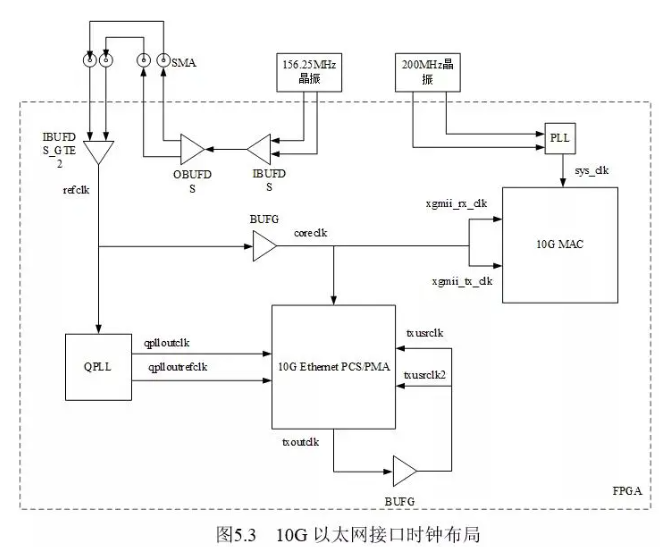

10G以太网接口分为10G PHY和10G MAC两部分。如下图所示。

本设计中使用了Xilinx公司提供的10GEthernet PCS/PMA IP核充当连接10GMAC的PHY芯片,然后将该IP核约束到光模块上构建完整的物理层。

需要说明的是本设计主要是完成以太网二层逻辑设计,不涉及PHY层的逻辑设计,如:bit同步、字节同步、字同步、64b/66b编解码等。

2、10G以太网接口PHY

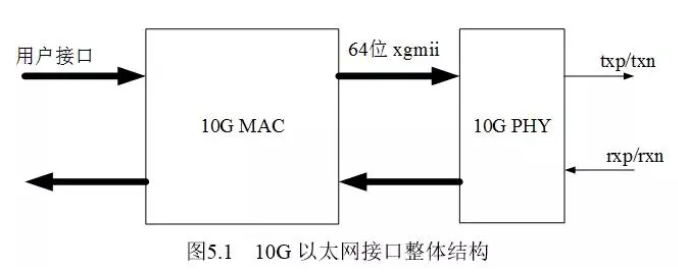

10G EthernetPCS/PMA的整体结构如图5.2所示,其核心是基于RocketIO GTH/GTX来实现的。从图中可知,该模块分为PCS层和PMA层,对于发送数据,

PCS层主要功能是对数据进行64B/66B编码、扰码、发送变速等功能。同时在测试模式下还提供了一个测试激励源,用于对链路进行检测。

PMA层的主要功能是提供并串转换、对串行信号进行驱动并发送等功能。对于接收数据,PMA层的主要功能是将接收到的高速差分信号进行串并转换、

bit同步、时钟恢复等功能,PCS层对于从PMA层接收到的数据进行块同步、解扰码、64B/66B解码、弹性缓存等。同时在测试模式下还提供测试激励检测功能,用于检测链路工作状态。

在接口调试过程中,可能用到PMA层的近端环回和远端环回功能。PMA近端回环,用于测试IP核内部自回环;PMA远端回环,

用于将接收到的远端10G PHY发送的的数据在PMA层直接回环发送给远端10G PHY,而不经过本地的PCS层。

3、10G以太网接口时钟布局设计

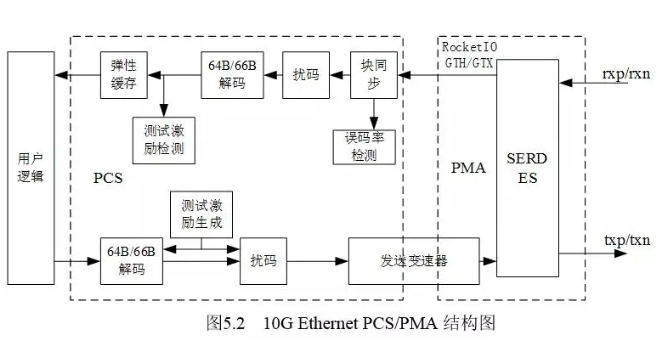

由于10G Ethernet PCS/PMA是Xilinx官方提供的一款IP核,所以我们需要做的工作是结合开发板的实际情况,

为该IP核以及其他模块设计合理的时钟电路,使其能够正常工作。本文选用Xilinx VC709开发板作为上板调试的硬件平台,

因此我们的时钟布局需要充分考虑此开发板的结构来设计,具体的时钟布局如图5.3所示。